Abstract: This paper proposes a remote dynamic reconstruction method for FPGA, which is realized by combining FPGA dynamic reconstruction technology and GSM communication technology. The GSM technology is used to realize the wireless transmission of the configuration data, and the data is stored in the CF card under the control of the single chip microcomputer. Under the control of the embedded hard-core microprocessor PowerPC405, the FPGA reads the new configuration data in the CF card through the internal configuration access port, and configures the reconfigurable area to implement new functions.

With the wide application of field programmable gate arrays, more and more research is being carried out on flexible reconfiguration. At present, most FPGAs are based on the lookup table LUT (Look UP Table) technology, which is produced by SRAM process. The FPGA of this process has a two-layer structure, the upper layer is the configuration memory, and the lower layer is the hardware logic layer. The upper layer configuration information is used to control the on and off of the hardware layer gate circuit, and the wiring of the basic logic block in the chip is changed to form a specific function. This architecture provides the possibility for dynamic refactoring technology implementation. An FPGA large-scale digital system is always composed of many functional modules, so that the activation state of each system module may be separated on the time axis, and the time-separated modules can share a hardware logic area, and this logical area is needed according to needs. Dynamically change the configuration to achieve different functions, this is the local dynamic reconstruction [1]. The dynamic reconfiguration of FPGAs makes them more flexible, reducing hardware resource consumption and shortening the development cycle. However, for some special occasions, such as deep sea data acquisition or robot field exploration, developers can design several functions for a certain system module. The equipment selects the corresponding configuration data for configuration during the autonomous operation. If you encounter a special environment, the pre-designed functions may not be suitable for the job requirements, and new functions need to be added. In the current situation that hardware evolution technology is still not practical, this paper designs a remote dynamic reconstruction system to solve the above problems.

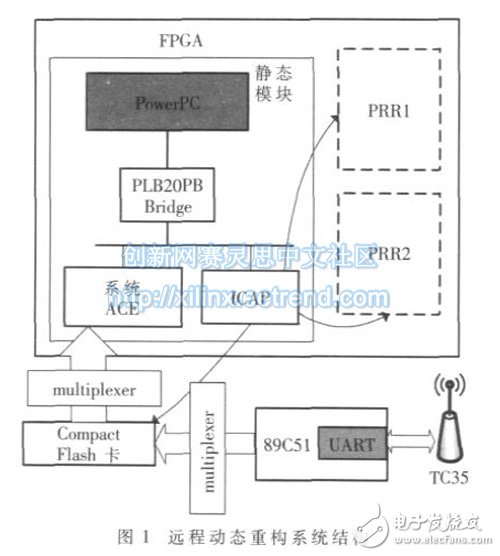

1 Remote dynamic reconstruction system structureThe remote dynamic reconfiguration system has two cores, the PowerPC processor and the 89C54 microcontroller. Virtex II -Pro FPGA integrates two PowerPC405 embedded processors [2]. This system uses one of them to control and configure dynamic reconfiguration. There are three hardware modules in the FPGA for reconfiguring the local reconstruction area PRR, namely the embedded kernel PowerPC, the system advanced configuration environment System ACE and the internal configuration access channel ICAP. System ACE is an advanced configuration solution for system programming. It provides multiple interfaces such as CF (Compact Flash), MPU and Test JTAG. This system uses CF card as the source of configuration data, which makes it easier to change and store the configuration. data. The primary role of ICAP is to reconfigure configuration data into the PRR at a specific timing [3].

The remote data transmission is completed by the external controller 89C54. On the one hand, the controller receives the data transmitted by the GSM module TC35 through the UART interface; on the other hand, the received configuration data is written into the CF card for reading by the FPGA system.

The System ACE and 89C54 controllers share the control interface of the CF card. In order to avoid mutual influence, the system uses a multiplexer to perform time-multiplexed processing on the CF card port, that is, it is connected to System ACE during configuration, and is connected to 89C54 during data transfer and storage. The structure of the remote dynamic reconfiguration system is shown in Figure 1.

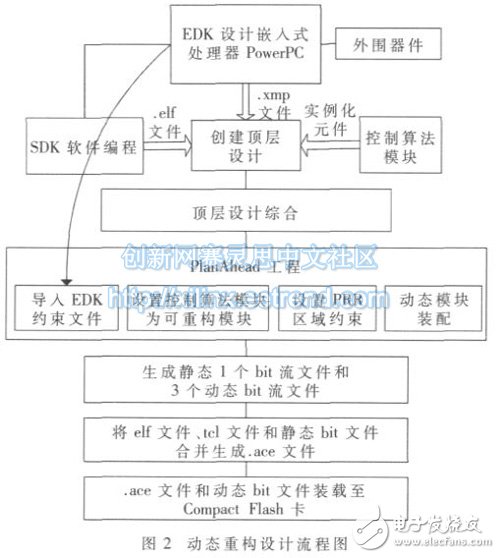

Taking the control of the robot arm as an example, PID control, fuzzy control: and standby three control schemes are adopted, and each control algorithm is verified and integrated to generate an independent bit stream module. These three modules share a reconfigurable area PRregion. According to the specific situation, the most suitable algorithm module is selected, and the reconstruction area is dynamically configured to control the robot arm, and other static logic areas are still running normally. This not only increases the flexibility of the system, but also saves configuration time and reduces unnecessary consumption. The design flow of FPGA generally includes design, simulation, synthesis, and implementation process. This paper proposes the design flow shown in Figure 2 according to the structure of the system itself.

The FPGA reconfiguration system uses a combination of EDK (Embedded Development Kit), ISE and PlanAhead tool platforms in a layered design to simplify the design process. The process is as follows:

(1) Design a PowerPC405-based embedded control system using the embedded development tool EDK [4], add the SystemACE_Compact-Flash peripheral to support the FPGA configuration from the CF card; add the IP core opb_hwicap to support the embedded kernel to read the configuration through ICAP The data dynamically configures the FPGA.

(2) EDK includes the software development tool SDK, so use the SDK to software program and debug the PowerPC405, and finally generate the application binary executable.elf file; use the EDK peripheral creation wizard to create multiple control algorithm IP modules, in their respective Write the corresponding algorithm in the VHDL file; use the ISE tool to synthesize multiple algorithm modules, create top-level modules, instantiate embedded systems, and algorithm modules. The top netlist file is generated comprehensively.

(3) Create a PlanAhead project, and use the netlist file and constraint file generated above for placement and routing. The most important of these is to set the algorithm module as a reconfigurable module, and impose strict regional constraints on it [5]. The constraint code is as follows:

AREA_GROUP "AL_PRregion" RANGE = SLICE_ (minX)

(minY): SLICE_(maxX)(maxY)

AREA_GROUP "AL_PRregion" RANGE = RAMB16_

(minX)(minY): RAMB16(maxX)(maxY)

Area constraints can be visualized in the PlanAhead tool, which is both intuitive and simple. If the reconfigurable module needs to implement different control algorithms during the running process, you need to add the netlist file generated by all the algorithm modules in the reconstruction area and use the PR Assemble command to generate multiple different algorithm bit stream files. In addition to the dynamic bitstream file, PlanAhead also generates a static complete bitstream file, staTIc_full.bit. The following two commands can be executed to generate an ace configuration file:

(1)data2mem -bm implementaTIon/system_stub_bd -bt implementaTIon/staTIc_full.bit -bd TestApp/executable.elf tag

Ppc310_0 – ob implementation/static.bit .

(2)xmd -tcl genace.tcl -jprog -target ppc_hw -hw

Implementation/static.bit -elf TestApp/executable.elf -board

Ml310 -ace system.ace.

Nervos is an ambitious newcomer on the crypto market and Changelly has long watched it with interest. The project attracted the attention of investors and developers since its purpose is not to launch another cryptocurrency in the ecosystem. Nervos is a simple connecting database between any blockchains.

Nervos was launched in November 2019 by Nervos Network and aims to fix issues that plague both Bitcoin and Ethereum. Among them are scalability and value differences. To fix them, the Nervos team wants to implement effective scalability and raise the cost of their token by hosting other cryptocurrencies on their blockchain. Nervos supports smart contracts and is censorship-resistant. CKB is a native token of the Nervos network. It scales with the value of other assets stored on the network: the more cryptos and tokens are there, the more valuable CKB becomes. This means that this token will continue raising its value the more attention and assets it attracts. Add to that the support of smart contracts, and you have a nice crypto bridge between different blockchains. Which is exactly what makes it so attractive for both crypto enthusiasts and investors.

ckb mining machine,eaglesong algorythm,ckb miner,goldshel ck6,goldshell ck5

Shenzhen YLHM Technology Co., Ltd. , https://www.hkcryptominer.com