First, the design goal of DC motor drive circuit

In the design of the DC motor drive circuit, the main considerations are as follows:

Function: Is the motor unidirectional or bidirectional? Does it need speed regulation? For one-way motor drive, just use a high-power triode or FET or relay to directly drive the motor. When the motor needs to rotate in both directions, it can be used. An H-bridge circuit consisting of 4 power components or a double-pole double-throw relay. If you do not need speed regulation, just use the relay; but if you need speed regulation, you can use PWM (pulse width modulation) speed regulation by using switching elements such as triode and FET.

Performance: For the PWM drive motor drive circuit, the main performance indicators are as follows.

1) Output current and voltage range, which determines how much power the circuit can drive.

2) Efficiency, high efficiency not only means saving power, but also reducing the heating of the drive circuit. To improve the efficiency of the circuit, it is possible to ensure the switching state of the power device and prevent common-state conduction (a problem that may occur in the H-bridge or push-pull circuit, that is, the two power devices are simultaneously turned on to short-circuit the power supply).

3) The effect on the control input. The power circuit should have good signal isolation at its input to prevent high voltage and high current from entering the main control circuit, which can be isolated with high input impedance or optocoupler.

4) The impact on the power supply. Common-state conduction can cause a transient drop in the power supply voltage to cause high-frequency power supply contamination; large currents can cause the ground potential to float.

5) Reliability. The motor drive circuit should be as close as possible, no matter what kind of control signal, what kind of passive load, the circuit is safe. Second, triode-resistor for gate drive

1. Input and level shifting section:

The input signal line is introduced by DATA, the 1 pin is the ground line, and the rest is the signal line. Note that 1 foot to ground is connected to a 2K ohm resistor. When the driver board and the microcontroller are powered separately, this resistor can provide a path for the signal current to flow back. When the driver board and the microcontroller share a set of power supplies, this resistor can prevent large currents from flowing along the wires that flow into the ground of the microcontroller board. In other words, it is equivalent to separating the ground line of the driver board from the ground line of the microcontroller to achieve "one-point grounding".

The high-speed op amp KF347 (also available as TL084) acts as a comparator that compares the input logic signal to a 2.7V reference voltage from the indicator and a diode and converts it into a square wave signal that is close to the power supply voltage amplitude. The input voltage range of the KF347 cannot be close to the negative supply voltage, otherwise an error will occur. Therefore, a diode that prevents the voltage range from overflowing is added to the input of the op amp. One of the two resistors at the input is used to limit current, and one is used to pull the input low when the input is left floating.

The LM339 or any other open-circuit comparator cannot be used in place of the op amp, because the high-level output impedance of the open-circuit output is above 1 kΩ, and the voltage drop is large, and the transistor of the latter stage cannot be turned off.

2. Gate drive part:

The circuit composed of the rear transistor and the resistor and the Zener tube further amplifies the signal, drives the gate of the FET and uses the gate capacitance of the FET itself (about 1000pF) to delay the FET of the upper and lower arms of the H-bridge. Simultaneous conduction ("common state conduction") causes a short circuit in the power supply.

When the output of the op amp is low (about 1V to 2V, it can't reach zero completely), the lower transistor is turned off and the FET is turned on. The upper transistor is turned on, the FET is turned off, and the output is high. When the output of the op amp is high (approximately VCC-(1V to 2V) and cannot fully reach VCC), the lower transistor is turned on and the FET is turned off. The upper transistor is turned off, the FET is turned on, and the output is low.

The above analysis is static. The following is a discussion of the dynamic process of switching: the on-resistance of the triode is much less than 2 kΩ, so the charge on the gate capacitance of the FET can be quickly released when the transistor is switched from off to on. Closed quickly. However, it takes a certain time for the transistor to be charged by a 2 kΩ resistor when the transistor is switched from on to off. Correspondingly, the FET switches from on to off at a faster rate than from off to on. If the switching action of the two triodes occurs at the same time, this circuit can make the FETs of the upper and lower arms break and then pass, eliminating the common-state conduction phenomenon.

In fact, the output voltage of the op amp needs to change for a certain period of time. During this time, the output voltage of the op amp is in the middle between the positive and negative supply voltages. At this time, the two transistors are turned on at the same time, and the FET is turned off at the same time. So the actual circuit is safer than this ideal situation.

A 12V Zener diode for the FET gate is used to prevent FET gate overvoltage breakdown. The voltage resistance of the general FET gate is 18V or 20V, and the voltage directly applied to 24V will break down. Therefore, this Zener diode cannot be replaced by a normal diode, but it can be replaced by a resistor of 2 kΩ. 12V partial pressure.

3. Field effect tube output part:

In the high-power FET, there is a diode connected in reverse parallel between the source and the drain. When connected to the H-bridge, it is equivalent to four diodes used to eliminate the voltage spike in the output terminal. Therefore, there is no external diode. Parallel connection of a small capacitor (between out1 and out2) at the output has certain advantages in reducing the peak voltage generated by the motor. However, there is a side effect of peak current when using PWM, so the capacity should not be too large. This capacitor can be omitted when using a low power motor. If you add this capacitor, you must use a high withstand voltage, ordinary ceramic capacitors may break through the short circuit.

The circuit consisting of a resistor and a light-emitting diode and a capacitor connected in parallel at the output end indicates the direction of rotation of the motor.

4. Performance indicators:

The power supply voltage is 15~30 V, and the maximum continuous output current is 5A/per motor. It can reach 10A in short time (10 seconds) and 30KHz in PWM frequency (usually 1 to 10KHz). The circuit board contains four logic independent units, and the output terminals are connected to form an H-bridge power amplification unit, which can be directly controlled by a single-chip microcomputer. Realize the bidirectional rotation and speed regulation of the motor.

5. Wiring:

The high-current line should be as short and thick as possible, and try to avoid passing through the via hole. If it is necessary to pass the via hole, make the via hole larger (>1mm) and make a small via hole on the pad. Solder fills up, otherwise it may blow. In addition, if a Zener diode is used, the source of the FET should be as short and thick as possible for the power supply and the ground. Otherwise, at high current, the voltage drop across the conductor may pass through the positively biased regulator and The turned-on transistor burns it. In the initial design, the source of the NMOS transistor was once connected to a 0.15 ohm resistor to detect the current. This resistor became the chief culprit in the continuous burning of the board. Of course, if you replace the voltage regulator with a resistor, there is no such problem.

In the 2004 Robocon competition, we mainly used this circuit for motor drive.

Third, the simple gate drive of the low voltage drive circuit

The maximum gate-source voltage of a typical power FET is about 20V, so in a 24V application, the gate-source voltage must not exceed 20V, which increases the complexity of the circuit. But in applications with 12V or lower, the circuit can be greatly simplified.

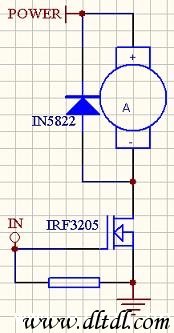

The left picture shows one side of a 12V transaxle, and the triode part of the upper circuit is replaced by two diodes and two resistors. (Note that the logic in the above diagram is reversed.) Due to the presence of the gate capacitance of the FET, charging the gate capacitor through R3 and R4 causes the FET to delay conduction; and directly discharges the gate capacitance through the diode to cause field effect. The tube is immediately cut off, thus avoiding common state conduction.

This circuit requires a square-wave pulse with a sharp edge at the IN input. Therefore, after the control signal is connected from a microcontroller or other open-output device, it must pass a Schmitt trigger (such as 555) or a high-speed comparator with push-pull output. Can receive the IN end. If the input edge is too slow, the diode delay circuit will lose its effect.

The selection of R3 and R4 is related to the rising and falling speed of the edge of the IN signal. The steeper the edge of the signal, the smaller the R3 and R4 can be selected, and the faster the switching speed can be made. In the boost circuit used in the Robocon game (similar in principle), the 555 is used before the IN.

Fourth, edge delay drive circuit

In the pre-stage logic circuit, the falling edge of the control PMOS and the rising edge of the control NMOS are deliberately delayed, and then the square wave is formed, and the common-state conduction of the FET can also be avoided. In addition, this can simplify the gate drive circuit of the latter stage, and can be a low-resistance push-pull drive gate, which does not need to consider the gate capacitance, and can be better adapted to different FETs. This drive circuit was used in the 2003 Robocon competition. The following figure is the delay circuit of two kinds of edges:

#FormatImgID_3#

The figure below is the corresponding NMOS, PMOS gate drive circuit:

#FormatImgID_4##FormatImgID_5#

The gate drive circuit consists of a two-stage transistor: the front stage provides the correct voltage required to drive the FET gate, and the latter stage is a level one emitter follower that reduces the output impedance and eliminates the effects of gate capacitance. In order to ensure that the common state is not turned on, the input edge should be relatively steep, and the above-mentioned circuit that delays and reshapes the above can be done.

Five other kinds of drive circuits

1. The idea of ​​relay + semiconductor power device

The relay has the advantages of large current and stable operation, which can greatly simplify the design of the drive circuit. In the motor drive circuit that needs to achieve speed regulation, the relay can also be fully utilized. One solution is to use relays to control the direction of the current to change the direction of the motor. Instead of using a single extra-large current FET (such as the IRF3205, which typically has only N-type extra-current tubes), PWM speed regulation is achieved, as shown in the right figure below. This is one way to achieve particularly high current drive. The reversing relay should use the double-pole double-throw type. The wiring is as shown in the left figure. The coil wiring is as follows:

#FormatImgID_6##FormatImgID_7# #FormatImgID_0#

2. Several driver chips

1) L298 Reference http://

2) A3952 Reference http://

3) A3940 Reference http://

4) L6203 Reference http://

Sixth, the realization of PWM speed regulation

1. Algorithm using timer

//butcher add it.

/ / Algorithm principle

/ / Programming implementation points

//Pros and cons

2. Algorithm using cyclic shift

The PWM signal can be generated by the timer, but since only two timers are provided in 51, if the signals of different duty ratios are to be output to three or more DC motors, the timer is set repeatedly, which is complicated. In a simpler way, we can not only provide different duty cycle input signals for more DC motors, but also occupy only one timer resource. This method can be simply expressed as follows:

Store the duty cycle information of the input signals required by each DC motor in a certain space of the memory. If the duty ratio is 1, save 0FFH (11111111B); if the duty ratio is 0.5, save 0F0H (11110000B) or any binary The number includes 4 zeros and 4 ones. which is

Number of duty = 1 / 8

The specific binary number to be selected depends on the output frequency requirements. To output the PWM signal to this DC motor, as long as each time slice is shifted once, the fixed one of the bits (which can be implemented by bit addressing or carry flag C) can be sent to the motor port. In addition, the shift algorithm is an algorithm that relies on previous results, so it is best to periodically check or reset the shifted number to prevent the error from being staggered.

The advantage of this algorithm is that it is an independent process, which can control multiple motors. The disadvantage is that it takes up a lot of resources and the PWM frequency is low.

3. Implementation of analog circuit PWM

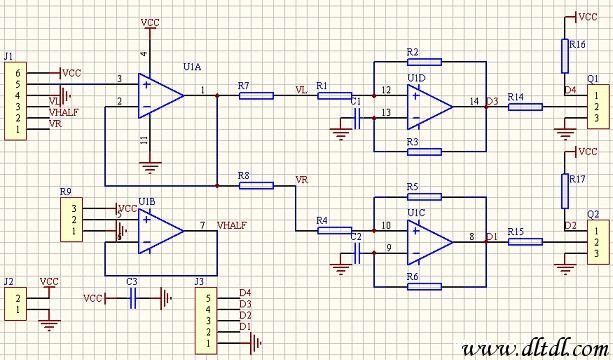

#FormatImgID_1#

The picture above shows a PWM generation circuit that controls the two chassis drive motors using a linear joystick (or linear Hall element) on the joystick or RC joystick. J1 is the socket of the handle, and 123 and 456 are potentiometers in both x and y directions. U1B provides a half supply voltage and U1A is a voltage follower. The x, y component is synthesized into a voltage signal that controls the speed of the two motors of the left and right wheels. In use, let L = (x + 1) y / (x + 1.4), R = (x-1) y / (x - 0.6), after testing has a good effect (the number is only the unit, not the voltage value) . The Schmitt oscillator consisting of U1C and U1D converts the voltage into a corresponding PWM signal for controlling the power drive circuit. Taking U1D as an example, R1 and R2 form a Schmidt circuit with hysteresis. The upper and lower thresholds are affected by the input voltage, and C1 and R3 form a delay loop. The pulse width of the oscillation is controlled by the input voltage. Q1, Q2 are triodes that form an inverter that provides differential control signals. See the analysis of the 555 oscillator for specific oscillations.

Seven, stepper motor drive

1. Low power 4-phase stepper motor drive

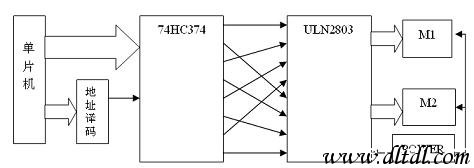

The following is a block diagram of the drive circuit:

#FormatImgID_2#

The Darlington tube array ULN2803 removes the 0th, 2nd, 4th, 6th and 1, 3, 5, and 7 bits from the latch to drive two stepper motors. The four-phase stepper motor can be energized in several orders. :A,B,C,D (4 phase 4 beats); AB, BC, CD, DA (4 phase double 4 beats); A, AB, B, BC, C, CD, D, DA (4 phase 8 beats) In order to balance stability, torque and power consumption, generally adopt 4-phase 8-shot mode. All these methods can be realized by cyclic shift (also have regular monitoring). In order to make 4-phase 8 beat easy to implement, latch The device and the drive part are cross-connected.

The stepper motor works in four-phase eight-shot mode (ie, the input signal of forward rotation is 1000→1100→0100→0110→0010→0011→0001→1001→1000), and there are four signal inputs for each stepper motor. In theory, the output signal to the port can control the operation of two stepper motors. The register cyclic shift parity bit is used as the driving end of two stepping motors respectively, and the idea is as follows:

LOOP: MOV A, #1110000B ; put 11100000 in the A register

RR A; right shift

AJMP LOOP ; loop right shift

Thus, the value stored in the register A has the following cycle 11100000 → 01110000 → 00111000 → 00011100 → 00001110 → 00000111 → 10000011 → 11000001 → 11100000, and the odd bits have the following cycles 1000 → 1100 → 0100 → 0110 → 0010 → 0011 → 0001 → 1001→1000, the even digits have the following cycle 1100→0100→0110→0010→0011→0001→1001→1000→1100. When A is output to the P0 port, the odd and even digits are the stepper motors we need. input signal.

In fact, the action of each motor is different. For this reason, we open a byte status byte for each motor in the RAM for cyclic shift. In each motor cycle, the byte of each motor is needed according to each motor cycle. Shift, and use the ANL instruction to synthesize the state of the two motors into one byte and output the A at this time while controlling the two motors.

The speed of the stepper motor is determined by the frequency of the drive pulse. The period of the shift is different, and the speed of the motor is different. The motor cycle mentioned above should take the greatest common divisor of various possible cycles. In other words, once The motor cycle is determined, and the period of each motor shift should be a multiple of it. In the program, the corresponding frequency division ratio is set for each motor's corresponding time, and one variable is added for one count: each motor If the count variable <frequency ratio value, the count variable is incremented by one; if it is equal, the shift is performed, and the count variable is cleared. This realizes the frequency division speed regulation, which allows multiple motors to operate at different speeds at the same time.

In addition, it can also be driven by the traditional look-up table. The program is slightly longer, but it is also relatively stable. This method is very suitable for three-phase stepper motors.

The UCN5804B/LB is a 4-phase stepper motor driver dedicated chip from Allegro. It integrates control logic, pulse distribution and power boost. It sets the rotation mode and direction by changing the level of several pins. To change the speed of rotation, which brings great convenience to complete complex actions and test stepper motor parameters.

2. Intelligent driving scheme for stepper motor

Stepper motors have the advantage of being able to be precisely controlled, but with high power consumption, low efficiency and low torque. If a high-power stepper motor is used, in order to reduce power consumption, PWM constant current control can be adopted. The basic idea is to use a high-frequency PWM with feedback to drive the constant current for each phase according to the output power requirements, and the overall current sequence is in line with the rotation order. When the torque is small, the current should be reduced in time to reduce power consumption. The circuit realized by the scheme can adopt an independent single chip microcomputer or a CPLD plus FET driving circuit and a current sampling feedback circuit.

Eight, Appendix: parameters of several IRF FETs

VGA Cable, VGA to VGA HD15 Monitor Cable SVGA M/M HD Cable Gold Plated Connectors Support 1080P Full HD for PC, HD TV, Projector, etc

Product Features

The VGA cable is widely used in VGA digital transmission mode connection, adapted to a variety of electronic devices 15PIN interface, such as computers, high definition DVD and computer monitors, projectors, high definition digital TV, rear projection, plasma TVs and other appliances Device cable.

Compatible with the resolution

VGA cable can automatically identify the resolution required to adjust the device to support 800 * 600/1024 * 768/1152 * 864/1280720/1280 * 768/1280 * 800/1280 * 9601280 * 1024/1360 * 768/1600 * 1200/1920 * 1080

Connectivity - VGA to VGA Cable Connector HD15 Male to Male.

[15-pin MALE VGA CABLE] Screw-in VGA cable with 15-pin male input and output for gaming, video editing and video projection.

[HIGH PERFORMANCE] Supports resolutions at 800x600 (SVGA), 1024x768 (XGA), 1600x1200 (UXGA), 1080p (Full HD), 1920x1200 (WUXGA), and up for high resolution LCD and LED monitors.

[FUNCTIONS] Links VGA-equipped computer to any display with 15-pin VGA port also known as RGB, DE-15, HD-15, DB-15, D-sub 15 and HDB-15, input and output.

[FERRITE CORES] The VGA to VGA cable equipped with ferrite cores that could minimize crosstalk, avoid electrical radiation interference and protect against electromagnetic interference (EMI) and radio frequency interference (RFI).

[SECURITY] The VGA cord engineered with molded strain relief connectors for durability, grip treads for easy plugging and unplugging, and finger-tightened screws for a secure connection.

Compute Cable,Notebook Cable,HDMI to VGA Cord,VGA Cable,HDMI Cable

UCOAX , https://www.ucoax.com