|

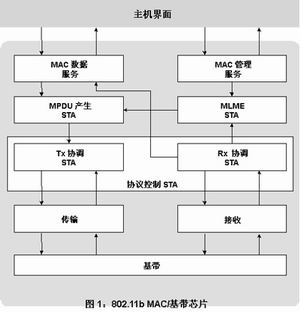

Figure 1: The 802.11b chip design integrates three components: MAC software, |

An abstract design model will be generated and simulated during the SoC system design cycle. This abstraction function is then mapped to the detailed architecture of the system and architectural performance modeling is performed. The architecture map divides the design into hardware and software to achieve its functionality. The hardware team implements the hardware portion of the design using Verilog or VHDL and uses a hardware emulator for verification. The software team encodes software modules in assembly language, C, or C++ languages ​​and uses either processor models or ICE test software. Traditionally, the software team had to wait for the hardware prototype to finish before being able to debug the software to achieve the final system integration.

Many problems often occur during system integration. These problems may be caused by such reasons as misunderstanding of specifications, inappropriate interface definitions, and final design changes. Errors can be eliminated by modifying the software or changing the hardware. The former may affect system performance. The latter may be very expensive and time consuming, especially when it comes to the redesign of the integrated circuit. Early system integration during the design cycle will help detect these integration issues early. This can be achieved by creating a hardware/software co-verification environment early in the design cycle.

Seamless hardware and software co-verification tools

A good hardware/software design and verification environment can discover functional and firmware (embedded software) issues and accelerate design convergence before silicon processing. Such a hardware/software design environment must be able to address the inherent shortcomings and limitations of typical hardware/software co-design tools and tool suites.

The seamless hardware/software co-verification tool provided by Mentor can verify the correct interaction between the hardware and software of the chip, and can determine the area for performance improvement. The Seamless tool accelerates the initial design implementation and verification process of the kernel-based SoC, increasing the chances of successful first-run tapeouts. The SeamlessCVE environment enables developers to create a variety of core-based virtual prototype verification platforms before getting physical prototypes. The ARM-based platform is one of such platforms and has been used in 802.11b chip design solutions. Developers can find and correct hardware/software interface errors early in the design cycle by implementing embedded software on simulated hardware. This reduces the possibility of hiding the problem into system integration when the software is completed and the design will be postponed due to error correction. The Seamless tool also allows developers to fully observe and control the operation of the hardware and software, thereby speeding up the debugging of the software, which is often a limiting factor in completing the system design process.

|

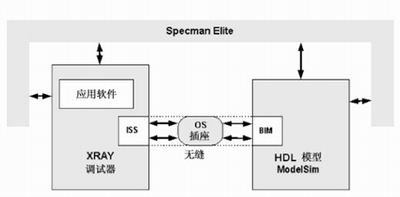

Figure 2: The 80211b chip co-verification environment. . |

The Seamless tool can run diagnostic code against virtual hardware. During software execution, ARM embedded processors generate millions of stored transactions, including instruction fetches and memory reads and writes. It will take several days to make millions of transactions through a logic simulator running at a speed of 10-20 clocks per second. The Seamless tool maintains a unique memory array for storage space that is accessed frequently by ARM processors. This allows developers to choose to implement access to specific memory ranges either through logic simulators or through interception by the Seamless tool.

The Seamless tool provides processor support kits for the ARM7, ARM9, ARM9E, ARM10, and ARM11 processor families. Each processor model consists of three components: an instruction set simulator (ISS), a graphical software debugger (XRAY), and a bus interface model (BIM) linking Seamless tools and an HDL or C hardware simulation environment. Seamless C-bridge technology supports the C hardware model to take full advantage of the faster simulation speed of the C hardware model than the HDL model.

The Seamless tool enables developers to see performance bottlenecks and understand how developers modify the design to eliminate the effects of these bottlenecks. It can display embedded CPU resource profile tables, stored transaction (including cache analysis) charts, bus load charts, and bus arbitration delay charts. The Seamless profile software can display the software function call sequence and duration using the Gantt chart, and can also display the embedded CPU time consumed by each software function call in the form of a histogram. Graphs showing the relationship between stored transactions and time can help highlight peak memory usage cycles and show how to better balance memory usage. Bus analysis shows that developers can see if the bus load and bus arbitration mechanisms are optimized.

802.11b chip verification

The 802.11b chip design integrates three components: MAC software, MAC hardware, and baseband processor (Figure 1).

The main MAC hardware blocks include the ARM7TDMI core, instruction code SRAM, and data storage space. MAC software implements two basic functions: data services and management services. At the same time, the MAC hardware implements transmission of MPDUs (Media Access Control Protocol Data Units) and reception of MPDUs.

The first step in running the Seamless tool is to map the ARM processor memory to a simulated storage instance in the hardware description. At this point any stimulus required by the hardware simulator has been determined. The Seamless ARM processor model can execute programs implemented in C/C++ and assembly language, and the application software does not need to be modified. Incentives include clocks, external interrupts, and serial data streams.

As shown in Figure 2, hardware designers can run application software without any modifications, and software engineers can test their software on virtual prototypes. The collaborative verification environment provides designers with a high level of design insight to execute software and track software execution on virtual prototypes. The code can be executed in the Xray debugger while monitoring the activity of the bus through the trace and list windows in the hardware simulator. Simulate execution by setting breakpoints.

|

Figure 3: Chip verification unit. |

Figure 3 shows the complete Specman Elite/Seamless integrated environment. Specman Elite can access software in addition to hardware. Using this feature, verification engineers can control the entire test environment and verify the system as a whole. The device under test (DUT) consists of the ARM7TDMI running MAC software and the corresponding MAC hardware devices. Hardware devices have input/output ports (four bits each), input/output 32/16-bit registers, and status/control registers. The hardware and software perform packet processing together. Mentor offers several patented performance optimization tool suites for the Seamless core, which can be used dynamically to significantly improve simulation speed performance.

This article summary

We are impressed by the effectiveness of Seamless collaborative verification. First, before getting a hardware prototype, using Seamless can verify that software and hardware work together, saving valuable time and engineering work. Second, using the Seamless Co-verification environment allows software engineers to identify all the major issues they find during traditional real-world hardware integration. As an innovative collaborative verification tool, the Seamless tool is a truly realistic and powerful method to help SoC design teams produce high-quality embedded chips.

Li-Ion 36V Battery,Lithium Ion 36V Battery,Lithium Ion Battery 36V 20Ah,36V Lithium Marine Battery, Super Batteries,LFP Battery, High rate lithium battery

Langrui Energy (Shenzhen) Co.,Ltd , https://www.langruienergy.com