With the rapid development of microelectronics technology and VLSI technology, the complexity of system design for electronic systems has been continuously increased, the heterogeneity of system software hardware has increased, and the proportion of software in the system has become larger and larger. . When designing electronic systems, traditional design methods are generally designed by the system engineer to design the entire system architecture, draw the system block diagram (including each module), and then use high-level programming languages ​​(generally C/C++/JAVA) to implement each module. The algorithm then simulates the entire system to determine the optimal structure, best implementation algorithm, and other relevant parameters of the system. After the system model is determined, the system software and hardware partition design is performed. However, due to the lack of a unified hardware and software co-design verification platform, most of the functions that should be completed by the software and hardware components can only be defined based on experience. For the function and behavior of the entire system, in the initial stage of design, the concept of fashion without hardware is divided. After the hardware and software are divided, the system specification description is divided into software implementation and hardware implementation.

There are two parts. Although languages ​​such as VHDL also support algorithm-level description, most Hardware Description Languages ​​(HDLs) such as VHDL, Verilog, etc. are basically hardware-oriented descriptions and are oriented to lower levels of hardware abstraction. At the same time, because the high-level programming language (C/C++/JAVA) cannot describe the physical information such as time, delay, and signal in the hardware design, and is incompatible with the subsequent hardware design, the hardware part needs to be designed again using hardware description languages ​​such as VHDL and Verilog. This caused a lot of design duplication and increased system design complexity.

In addition, many functions to be implemented in hardware, such as fast Fourier transform FFT, scanning line algorithm, blanking algorithm, and other mature and commonly used algorithms, have ready-made and perfect C language descriptions. If these resources can be reused, it will save a lot of System design time.

Many EDA tools only understand the description of the HDL language. It is the interface between the designer and the system. The designer tells the EDA tool through the HDL language and simulates, synthesizes, and verifies with the help of the EDA tool. Therefore, the description of the C language in the system design must be converted to HDL language to be accepted by the EDA tool. Among many HDL languages, VHDL language is widely used, so designing and implementing a compiler that converts from C language to VHDL language is of great significance and great practical value.

C language is a computer high-level language widely popular in the world. It is suitable as a system description language and can be used to write system software as well as application software. C language is developed on the basis of B language, which not only maintains the advantages of B language (concise, close to the hardware), but also overcomes its shortcomings (too simple, no data, etc.). Later, the C language was improved several times. Since 1978, C language has been ported to large, medium, small, and micro-computers, and is independent of UNIX and PDP.

In 1983, the American National Standardization Institute (ANSI) integrated and expanded various versions of the C language and developed a new standard called ANSIC. In general, C language is suitable for describing the process and algorithm, and its operating environment is the Turing machine model. It has a lot of flexible description methods, has a high abstraction ability, and does not distinguish between functions and processes. The definition of the array and the flexible application of the pointer greatly facilitate the writing of the program, and because it is a language designed for the development of software, it is better at describing serial programs. However, because it cannot reflect the physical characteristics such as time, delay, and signal in the hardware design, the hardware module part needs to be re-designed with the hardware description language, and the follow-up design lacks consistency, which also increases the complexity of the system design.

VHDL (Very-High-Speed ​​Integrated Circuit Hardware De2scripTIonLanguage) language is widely used as a hardware description language. It is defined as a standard hardware description language by the IEEE (The Institute of Electricland Electric Engineers) and the US Department of Defense, and is supported by many EDA companies in the field of electronic engineering. Has become a de facto universal hardware description language. VHDL can describe the structural characteristics of the circuit in a structured and hierarchical manner. It can also represent the relationship between the input and output signals of the circuit, and can also describe the geometric characteristics related to the layout of the chip. It is a more structured language suitable for describing concurrent programs. However, since its original purpose was not to design the circuit but to describe the circuit, it is not suitable for system-level software design and algorithm design, especially when more and more functions in the system are now completed by software.

DesignC language and VHDL language are two languages ​​that face different fields and have their own strengths. Designing and implementing a C to VHDL compiler is the description of the behavior of the C language algorithm to be translated into VHDL language. In order to complete the conversion from C language to VHDL, first use Lex and Yacc to complete lexical analysis and grammar analysis. A syntactical tree of C is generated at the time of parsing, and synthetic attributes are collected in the process of generating a syntactic tree from bottom to top. At the same time, semantic analysis is carried out in this process—only analyzing and translating the information related to the translation and translation. The semantics related to the C language itself are not analyzed, such as whether variables are repeatedly defined. In the expansion process of the syntax tree, the inherited attributes are passed down and transformed, and the protocol rules of C are translated into the corresponding VHDL protocol rules.

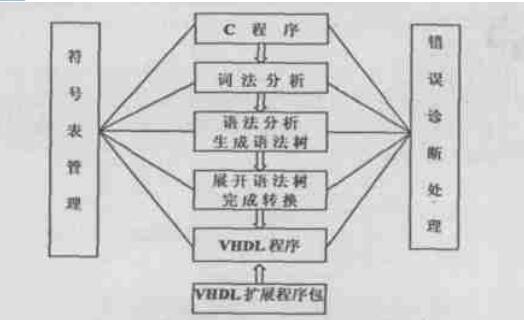

Figure 1C to VHDL Compiler Implementation

The specific design and implementation of the compiler are shown in Figure 1. Generate a syntax tree in the process of parsing—a multi-branch tree whose leaf nodes record words in C programs and records the position, attributes, and values ​​of words, non-leaf nodes record the rules of C language conventions, and Passed attributes—including synthetic and inherited attributes.

Because C language is more flexible and VHDL language is more regular, only a certain range of more commonly used C language syntax subsets are selected for conversion; because VHDL can only be implemented by a synthesizable subset, it is necessary to consider synthesizable subsets when converting. The limitations; and VHDL language data types are limited, we must write VHDL package extended data types, in the expansion of the syntax tree to complete the conversion process used to describe the complex logic.

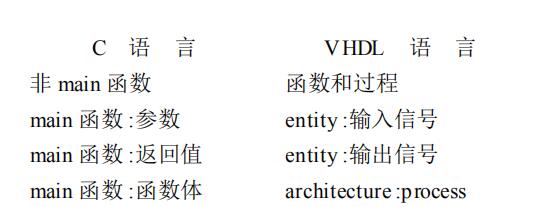

Conversion processSince C language is good at describing serial programs and VHDL is suitable for describing concurrent programs, the non-main functions in C programs are converted to functions (with return values) and procedures (without return values) in VHDL; for the main function, The parameter of the main function is used as the input signal of enTIty, and the return value of main is used as the entity

The output signal, the main function body as a process of the architecture. Although VHDL usually describes concurrent programs, its subroutines and processes are still executed sequentially, consistent with the original description of the C language. The specific function corresponding to the situation in Table 1.

In the conversion process, by analyzing the differences between the two languages, there are some unique and flexible description methods for C language— pointers, type conversions, concatenations, processing of i++ and ++i, arrays, and comma expressions. Correct translation is more critical and important.

For pointers in the C language, it is more difficult to fully translate its role in the C language to VHDL because pointers in the C language are essentially related to the allocation of addresses and memory. VHDL, as a language for describing hardware, does not have the concept of an address. Therefore, in the concrete conversion, the pointer type is translated into an integer type, and the name of the pointed array is recorded. The integer value indicates the number of elements in the array. Since C's high-dimensional pointers are obtained through memory allocation, they are difficult to implement in VHDL. Therefore, one-dimensional pointers are implemented initially, and C programs with high-dimensional pointers can be converted to one-dimensional pointers.

For i++ and ++i, when translating i++, it is first recorded which variables to go through this type of operation and then processed after the translation of the expression is completed. In translating ++i, because the value of the variable changes immediately, a complete expression must be separated when translating and a temporary variable must be introduced to handle the translation.

Compared to the flexible type conversion in C language, VHDL is more strict and does not allow operation between different types. Since the C language does not have a boolean type and the VHDL language has a boolean type, an integer or other type of number is converted to a boolean type in a conditional expression. At the same time, when dealing with logical operations of integers in C, it is necessary to convert the integers to VHDL Bit-Vectors, and then calculate them and convert them back.

In addition, since C language does not distinguish between functions and procedures, VHDL is strictly distinguished, and functions can only appear in expressions. Therefore, for function calls that do not appear in expressions, they must be translated in a temporary expression. , assigned to a temporary variable.

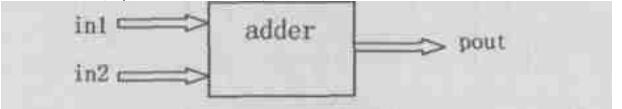

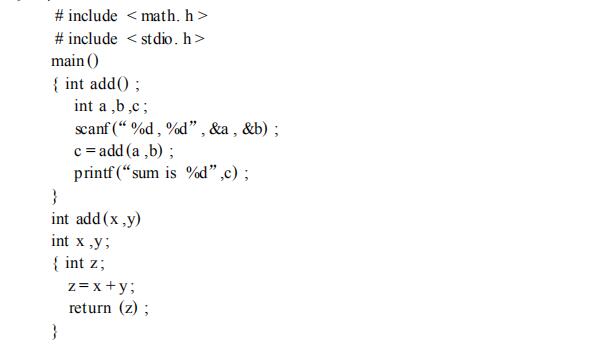

Testing and analysisIn order to test the correctness and effectiveness of the proposed design scheme, some commonly used digital circuit systems were selected in the design process to compare the functional consistency of the C source program and the VHDL object program. For example, for an adder circuit without a control port, the circuit diagram is shown in Figure 2

The adder does not have any control ports, there are two input ports in1 and in2, and one output port pout, all of which are bit vectors. When any or both of the input signals change, the process must be executed again. From the point of view of the circuit function, as long as there is a new data input at the input, the adder must restart the work and add the new value to the output port so that the addition operation continues. The C language for the adder circuit is described below

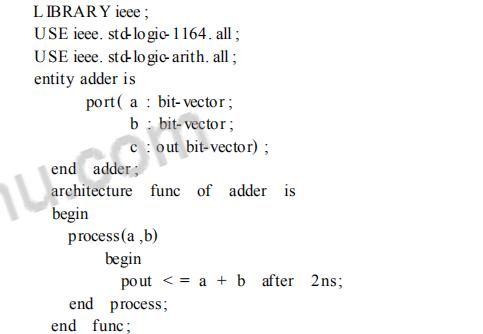

Use the design proposal proposed in this paper to compile and convert the C language program that implements the adder function to obtain the converted target program—the VHDL program is as follows:

By analyzing the semantics and functions of the compiled and translated target program, the conversion scheme is proved to be correct and effective. Due to the use of C language for algorithm and program design, it can greatly improve the level of system description and system design efficiency, and there are a large number of mature and perfect algorithms described in C can be reused, and VHDL language is accepted by most EDA tools. Hardware description language, so designing and implementing a compiler that converts from C language to VHDL language is of great significance and great practical value.

This paper analyzes the language features of C and VHDL and their respective advantages and disadvantages, proposes a reasonable and effective conversion scheme, points out several aspects that need to be paid attention to when converting from C to VHDL, and tests and analyzes the design scheme. the result of.

9V Power Adapter,Dc 9V Power Adapter,Adapter Dc 9V,9V 8A Adapter

ShenZhen Yinghuiyuan Electronics Co.,Ltd , https://www.yhypoweradapter.com