CCD (Charge Coupled Devices) is a new type of semiconductor device developed in the early 1970s. At present, CCD as a photoelectric sensor is widely used in camera materials because of its advantages such as small size, light weight, low power consumption, low operating voltage and anti-burnout, as well as resolution, dynamic range, sensitivity, real-time transmission, and self-scan , Meteorology, aerospace, military, medical and industrial testing and many other fields.

We need to collect and store a large amount of high-speed image data acquired by the CCD camera for subsequent processing and application. Before performing this series of signal processing, the acquisition of the target signal and the quality of the acquired signal are related to the debugging of the entire camera system. The essential. When debugging the camera system, because the debugging system always has some imperfect factors, and because multiple debugging will increase the risk cost of the CCD chip, especially for the more expensive CCD chip, if it is used frequently during debugging, it will bring There is a risk of damage, so the analysis and simulation of the output signal of the CCD chip during the debugging process has become an extremely important task. This paper designs a programmable wideband, high precision CCD signal generator based on CPLD. Make full use of the programmability of CPLD, simulate the CCD acquisition signal in various complex environments, while meeting the system's waveform and timing requirements, the output signal frequency reaches 11MHz.

2 Analysis of the characteristics of the CCD output signalThe output sequence of a CCD signal starts with a reset pulse. When the FET switch is closed, the voltage on the sensor capacitor in Figure 1 is the initial reference voltage value. This reference voltage value is called the reset feedthrough level. After a certain feed-through delay time, this voltage value decreases and becomes the true reset level. At this time, the FET switch is turned on, the pixel charge is transferred to this capacitor, and the voltage value on the capacitor is changed accordingly. This voltage value is the superposition of reference level, pixel level and some noise. When the CCD starts to work to read the effective signal, the output signal is reset at the rising edge of each reset signal, that is, the reset interference pulse 1 appears on the output signal, and then returns to the reference level 2, and the integration is obtained after reading. Pixel signal 3. The actual pixel width is 3, the width of 1, 2, and 3 is one pixel period, and the signal amplitude of each pixel is the height difference between 2 and 3. These are important parameters of the CCD output signal. The signal output by the CCD contains a large DC component. The DC bias voltage is indispensable for the normal operation of the CCD. Its value varies from a few volts to dozens of volts, and it consumes only a few milliamperes of current. Voltage and capacitance filtering.

Figure 1 CCD output signal

3 Hardware structureThe whole system is composed of three parts: digital signal generation module, digital-analog conversion module and output processing module. Select CPLD to form the signal generation module, make full use of its programmability, construct the CCD to collect data in various complex environments, and at the same time generate control signals matching the data signals to control the work of the lower-level digital-analog conversion module. The digital-to-analog conversion module receives the data and control signals sent by the superior and converts the data into analog signals for output under the control of the control signals. Since the conversion output of the module is current, an additional conversion module is needed to convert the current into the voltage signal required by the system. At the same time, in order to meet the system's signal accuracy requirements, active and passive filter circuit modules also need to be added. The system block diagram is shown in Figure 2. The crystal oscillator is used as the CPLD clock signal (clk) input, and other signals are generated by it.

Figure 2 System functional block diagram

The main work is divided into the following aspects:

(1) Signal generation module

The VHDL language is used to design the CCD to output image signals and timing control signals. The output signals include analog digital image signals (10-bit parallel output) and timing control signals, which mainly include: related double sampling signals, timing pulse signals required for A / D sampling , Line, field sync pulse signal, etc.

(2) Digital-to-analog conversion module

The analog digital signal is obtained through a digital-to-analog converter. The high-speed digital-to-analog conversion device is generally a current check output, so subsequent processing of the output analog signal is required.

(3) Output processing module

The analog signal output by the DAC is converted into a voltage output signal by an operational amplifier, and further processed to obtain a CCD output signal that meets the requirements.

4 Design of signal generation module CPLD4.1 Select the CPLD that meets the requirements

This design uses the ispLSI1032e CPLD from LATTICE. The chip has a total of 84 pins. The number of available gates reaches 6000 and 192 logic units. It can be individually configured for input, output and bidirectional operation. 64 general-purpose I / O ports. The transmission delay is 7.5ns, and the maximum working rate is up to 125MHz, which can meet the requirements of this design. The output frequency required by this system is a correlated double-sampling form of CCD signal of 11MHz, and there are strict requirements on the timing of the signal. A 66MHz crystal oscillator is selected as the clock input of the CPLD.

4.2 Programming

The output digital signal should be provided to the next-level sampling system of the image sensor, which meets certain timing requirements. The required timing pulse signal is sampled. The output signal has an analog CCD output signal and related double sampling signals, so A / D acquisition synchronization is required. Pulse signal, etc. In the CPLD part of the signal generation module, in addition to generating all the digital signals, we also need to prepare the required data and D / A clock timing for the next part of the digital-to-analog conversion module.

After using VHDL language to program, simulate and debug under isp environment, several simulated grayscale images and line and field synchronization signals are obtained. The output signals are digital image signals (10-bit parallel output), D / A clock signal (clock1) and write signal (wrt), related double sampling signals, line and field synchronization pulse signals, etc. The input clock signal (clk) is 66MHz, and the row synchronization signal row is used to ensure the synchronization of the output pixels.

Its output is used as the clock input of the analog CCD data generation and D / A conversion control module. The square wave signal ccdout [9..0] output from the analog CCD data generation module is converted to the analog output signal of the CCD after DAC conversion. The D / A conversion control module generates the DAC write signal WR and clock signal CLK, and requires D / A to sample and convert the high and low levels once in a cycle of data ccdout [9: 0], and requires wrt and clock1 in ccdout [9. .0] The high and low levels are sampled separately. In order to ensure the phase relationship between clock1 and the wrt signal, the wrt signal is transformed on the rising edge of clk, and the clock1 signal is transformed on the falling edge of clk. This produces the data and data we need. control signal.

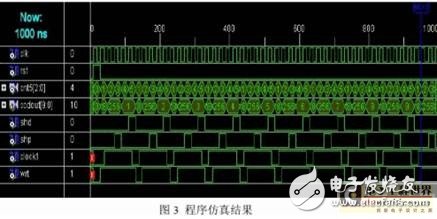

4.3 Simulation results

This design realizes the use of VHDL hardware programming language and CPLD to generate the data source signal of the system, including a set of digital signals before the analog signal output by the analog CCD and the control timing required for the next level, ensuring the system output signal The relationship between speed and phase. As shown in the simulation waveform of FIG. 3, ccdout [9..0] is an analog image signal, shp and shd are related double-sampling signals, and clock1 and wrt are the control signals of the next-stage digital-to-analog conversion module D / A. The reference pulse shp and the video pulse shd are sampled once at a pixel interval. The final output signal is the difference between the collected reference level and the video level. The relevant double sampling technique can be used to filter the superimposed on the output signal. Reset noise.

DAC2900 is selected as the digital-to-analog converter to convert the analog gray-scale image to the analog signal obtained by digital-to-analog conversion. DAC2900 is a 10-bit high-speed D / A device produced by TI. DAC2900 operates on a single power supply with a power supply range of 3.3-5V. DAC2900 is a current output digital-to-analog converter. It provides differential current output and can support single-ended or scoring applications. The matching of the two output currents ensures that the dynamic performance is improved in the differential output structure. The current output can be directly connected to the output resistor to provide two complementary single-ended voltage outputs or can be directly input to the transformer.

The analog signal output of DAC2900 can adopt single-ended output mode or differential output mode. The connection of single-ended output mode is relatively simple, but the anti-noise performance is poor, so the differential output mode is adopted to minimize signal noise and electromagnetic interference.

It adopts the differential output mode, which can basically cancel all even harmonics through the positive and negative input signals.

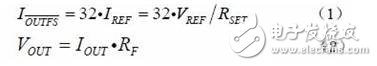

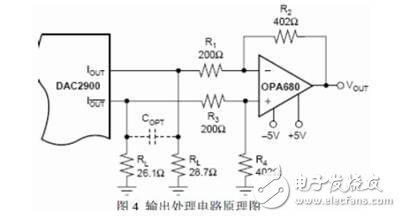

The schematic diagram provided by the DAC2900 chip data is shown in Figure 4, and the reference formula for the configuration scheme is as follows:

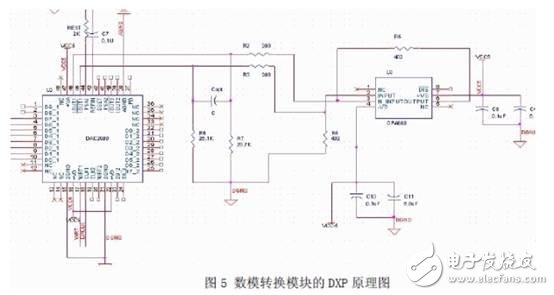

V is the internal + 1.25V reference voltage of DAC2900, SET R is the configuration resistance value introduced by DAC2900 from the outside. It can be known from formula (1) that OUTFS I can be adjusted by setting this resistance value, which is obtained by formula (2), thus The magnitude of the voltage OUT V can be controlled. The value of SET R in this system is 2K Ω, and a full-scale output of 20mA can be obtained. The system requires that the conversion voltage range is 0-500mV, and the output resistance FR takes a value of 25 Ω to meet the system requirements. Using CADENCE software to achieve PCB design, the schematic diagram is shown in Figure 5:

After the above-mentioned digital signal generation, digital-to-analog conversion and conversion, you can basically get the required signal waveform with a frequency of 11 MHz. A lot of high-frequency noise is superimposed on the signal, which cannot meet the low-noise requirements of the lower sampling system. Therefore, it is necessary to improve the signal from multiple angles such as PCB layout, wiring and device configuration to limit the noise to less than 10 mV, mainly to improve system performance and suppress noise from the following three aspects:

(1) Power filter part. The power supply noise is the most harmful. The power supply noise is filtered by adding a filter circuit to the power supply. At the same time, because the large bypass capacitor may fail due to resonance, some smaller bypass capacitor arrays are arranged on the circuit board. Each power supply voltage pin must be connected with 0.1μ, capacitor to filter.

(2) Since the system works at a higher frequency, it is necessary to consider the problem of signal integrity, that is, to solve the problems of signal reflection and crosstalk between signals. Choose the method of series termination and place the matching resistor as close to the signal sending end as possible. At the same time, the designed PCB drawing is imported into CADENCE software for simulation to determine the best series resistance value. After the actual system passes the series matching resistance, the overshoot and ringing of the signal are effectively eliminated.

(3) Add analog first-order active filter circuit. It is found through the oscilloscope that high-frequency noise is superimposed on the generated signal. In order to filter this noise, an OPA680 amplifier is used to form an active low-pass filter circuit. By adjusting the device parameters to change the low-pass frequency range of the filter, it greatly facilitates system debugging and effectively filters out high-frequency noise. Adding an RC low-pass filter circuit to the connector pins has actually proved to have a certain improvement effect on improving the signal quality.

7 ConclusionAfter the compilation and simulation are passed, the schematic diagram is used for comprehensive implementation on the top layer, and then the chip is burned in for experimentation, and the design is improved according to the actual operating conditions. According to the delay characteristics of the actual device. Insert appropriate delay units in certain places in the design to ensure that the delays are consistent. This design completes the CCD output signal simulation and gives the final simulation waveform. We tested the output signal of the designed signal generator under different configuration data. The waveform and signal-to-noise ratio of the signal can fully meet the performance indicators required by the system, which shows that the design scheme is effective.

Innovation: This article designs a programmable high precision CCD signal generator based on CPLD. Make full use of the programmability of CPLD. The CD signal that meets the system requirements is simulated, and the output signal frequency reaches 1IMHZ.

Stainless Steel Shaped Line,Surgical Steel Wire,Flux Core Stainless Steel Mig Wire,Stainless Steel Tig Welding Rods

ShenZhen Haofa Metal Precision Parts Technology Co., Ltd. , https://www.haofametals.com